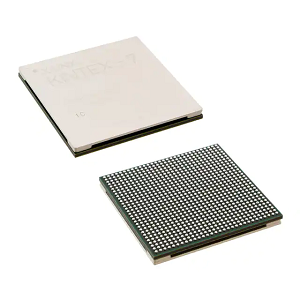

XC7K420T-2FFG901I – Samþættir hringrásir, innbyggðar, forritanlegar hliðarflokkar

Eiginleikar vöru

| GERÐ | MYNDATEXTI |

| flokki | Integrated Circuits (ICs)Innfelld Field Programmable Gate Arrays (FPGA) |

| framleiðanda | AMD |

| röð | Kintex®-7 |

| vefja | bakki |

| Staða vöru | Virkur |

| DigiKey er forritanlegur | ekki staðfest |

| LAB/CLB númer | 32575 |

| Fjöldi rökfræðilegra þátta/eininga | 416960 |

| Heildarfjöldi vinnsluminni bita | 30781440 |

| Fjöldi I/Os | 380 |

| Spenna - Aflgjafi | 0,97V ~ 1,03V |

| Gerð uppsetningar | Yfirborðslím gerð |

| Vinnuhitastig | -40°C ~ 100°C (TJ) |

| Pakki/Húsnæði | 900-BBGA, FCBGA |

| Hjúpun seljanda íhluta | 901-FCBGA (31x31) |

| Vörustjóranúmer | XC7K420 |

| GERÐ | MYNDATEXTI |

| flokki | Integrated Circuits (ICs)Innfelld |

| framleiðanda | AMD |

| röð | Kintex®-7 |

| vefja | bakki |

| Staða vöru | Virkur |

| DigiKey er forritanlegur | ekki staðfest |

| LAB/CLB númer | 32575 |

| Fjöldi rökfræðilegra þátta/eininga | 416960 |

| Heildarfjöldi vinnsluminni bita | 30781440 |

| Fjöldi I/Os | 380 |

| Spenna - Aflgjafi | 0,97V ~ 1,03V |

| Gerð uppsetningar | Yfirborðslím gerð |

| Vinnuhitastig | -40°C ~ 100°C (TJ) |

| Pakki/Húsnæði | 900-BBGA, FCBGA |

| Hjúpun seljanda íhluta | 901-FCBGA (31x31) |

| Vörustjóranúmer | XC7K420 |

FPGA

Kostir

Kostir FPGA eru sem hér segir:

(1) FPGAs samanstanda af vélbúnaðarauðlindum eins og rökfræðilegum frumum, vinnsluminni, margfaldara osfrv. Með því að skipuleggja þessar vélbúnaðarauðlindir á skynsamlegan hátt er hægt að útfæra vélbúnaðarrásir eins og margfaldara, skrár, heimilisfang rafala osfrv.

(2) Hægt er að hanna FPGA með því að nota blokkarmyndir eða Verilog HDL, frá einföldum hliðarrásum til FIR eða FFT hringrása.

(3) FPGA er hægt að endurforrita endalaust, hlaða nýja hönnunarlausn á örfáum hundruðum millisekúndna, með því að nota endurstillingu til að draga úr kostnaði við vélbúnað.

(4) Rekstrartíðni FPGA er ákvörðuð af FPGA flísinni sem og hönnuninni og hægt er að breyta henni eða skipta út fyrir hraðari flís til að uppfylla ákveðnar krefjandi kröfur (þó að rekstrartíðnin sé auðvitað ekki ótakmörkuð og geti vera aukinn, en stjórnast af núverandi IC ferlum og öðrum þáttum).

Ókostir

Ókostirnir við FPGA eru sem hér segir:

(1) FPGAs treysta á vélbúnaðarútfærslu fyrir allar aðgerðir og geta ekki innleitt aðgerðir eins og greiningarskilyrt stökk.

(2) FPGA geta aðeins innleitt fastapunktaaðgerðir.

Í stuttu máli: FPGAs treysta á vélbúnað til að útfæra allar aðgerðir og hægt er að líkja þeim við sérstakar flísar hvað varðar hraða, en það er stórt bil í hönnunarsveigjanleika miðað við almenna örgjörva.

Hönnun tungumála og vettvanga

Forritanleg rökfræðitæki eru vélbúnaðarberar sem konkretisera staðfestar aðgerðir og tækniforskriftir rafrænna forrita með EDA tækni.FPGA, sem eitt af almennu tækjunum sem útfæra þessa leið, eru beinlínis notendamiðuð, afar sveigjanleg og fjölhæf, auðveld í notkun og fljót að prófa og innleiða í vélbúnaði.

Hardware Description Language (HDL) er tungumál sem notað er til að hanna stafræn rökkerfi og lýsa stafrænum hringrásum, þau helstu sem almennt eru notuð eru VHDL, Verilog HDL, System Verilog og System C.

Sem alhliða vélbúnaðarlýsingartungumál hefur VHDL (Very High Speed Integrated Circuit Hardware Description Language) þá eiginleika að vera óháð tilteknu vélbúnaðarrásinni og óháð hönnunarvettvangi, með kostum víðtækrar lýsingargetu, ekki háð sérstökum tækjum og getu til að lýsa hönnun flókinnar stjórnunarrökfræði í ströngum og hnitmiðuðum kóða o.s.frv. Það er stutt af mörgum EDA fyrirtækjum og hefur verið mikið notað á sviði rafrænnar hönnunar.mikið notað.

VHDL er háþróað tungumál fyrir hringrásarhönnun og samanborið við önnur lýsingartungumál vélbúnaðar hefur það einkenni einfalts tungumáls, sveigjanleika og óháð tækjahönnun, sem gerir það að algengu vélbúnaðarlýsingartungumáli fyrir EDA tækni og gerir EDA tækni meira aðgengileg hönnuðum.

Verilog HDL er mikið notað vélbúnaðarlýsingarmál sem hægt er að nota á mörgum stigum vélbúnaðarhönnunarferlisins, þar á meðal líkanagerð, myndun og uppgerð.

Kostir Verilog HDL: svipað og C, auðvelt að læra og sveigjanlegt.Hástafa-næmur.Kostir í ritörvun og líkanagerð.Ókostir: ekki er hægt að greina margar villur við þýðingu.

VHDL Kostir: Stíf setningafræði, skýr stigveldi.Ókostir: langur kynningartími, ekki nógu sveigjanlegur.

Quartus_II hugbúnaður er fullkomið hönnunarumhverfi á mörgum vettvangi þróað af Altera, sem getur mætt hönnunarþörfum ýmissa FPGA og CPLD og er alhliða umhverfi fyrir forritanlega kerfishönnun á flís.

Vivado Design Suite, samþætt hönnunarumhverfi gefið út af FPGA söluaðilanum Xilinx árið 2012. Það felur í sér mjög samþætt hönnunarumhverfi og nýja kynslóð verkfæra frá kerfi til IC stigs, allt byggt á sameiginlegu skalanlegu gagnalíkani og sameiginlegu villuleitarumhverfi.Xilinx Vivado Design Suite veitir FIFO IP kjarna sem auðvelt er að nota á hönnun.